注目ベンチャー紹介:Cognichip

2025

.

12

.

15

Written by Yuhei Yano

今回の注目ベンチャーの紹介はCognichipです。

同社は、半導体設計プロセスのフロントエンドからバックエンドまでをカバーする”AI Copilot"を開発しています。

Cognichip

サービス/プロダクト概要

- 半導体設計プロセスを根本的に再発明することを目指す AI スタートアップであり、同社が提唱する Artificial Chip Intelligence(ACI®) は、「チップ設計を理解し、推論し、学習し、自ら最適化できる“チップ版 AGI(汎用AI)」という新しいカテゴリーの基盤モデル(foundation model)を目指している。

- (現在はACIを活かしたCopilotにイメージが近い)

- ACI® は、これまで分断されてきた以下の設計情報を同一の意味空間で扱うことができる:

- プロダクト仕様(テキスト)

- 論理アーキテクチャ設計

- RTL コード生成

- 合成後ネットリスト(回路グラフ)

- 物理設計(レイアウト/GDS)

- 検証結果・レポート(ログ・解析データ

- これらを統合的に理解することで、設計の生成、分析、修正、検証、FPGA/ASIC向けキャストまでを AI が支援・自動化するという世界観を実現することを目指す。

- 同社のプロダクト群は次の5レイヤーで構成される

- DRAGON™:Physics-informed foundation model

- COGNISOLVE™:RTL・テストベンチ生成、設計推論エンジン

- COGNICAST™:FPGA/ASIC 向けのキャスト(マッピング)エンジン

- COGNIX™ Chip OS:プロセスPDK/ライブラリ/IPを統合管理する抽象レイヤー

- COGNIFY™:会話 UI による設計フロントエンド

- これにより、従来の“直列ウォーターフォール型”設計を “サイクル型かつ並列的なAI駆動フロー” へ転換することができる

特徴/提供価値

1.設計時間を50%以上短縮

- 従来は仕様策定 → RTL → 検証 → 物理 → 再修正…という線形フローで数年を要したプロセスが、ACI® により 同時並列で最適化されるため大幅に短縮可能

2.開発コストを最大75%削減

- 検証作業(通常 70% の工数)が AI により効率化。さらに設計者数も削減可能で、総合コストを劇的に軽減可能。

3.“設計者レベル”の認知能力を持つ AI

- Cognichip のモデルは、設計者が暗黙的に理解してきた以下の概念を学習:

- 回路の階層性

- タイミング制約

- レイアウト上の物理的制約

- IP再利用・組み立て

- 仕様と実装の整合

- これは単なる LLM ではなく、専門領域に特化した physics-informed モデルである

4.ウォータフォール型から“サイクル型”設計へ

- アーキテクチャ・ロジック・検証・電力・サイズ・テスタビリティを並列に最適化できることを示唆。

ビジネスモデル

サブスクリプション/ユーザー を想定。

市場動向・なぜこの会社なのか?

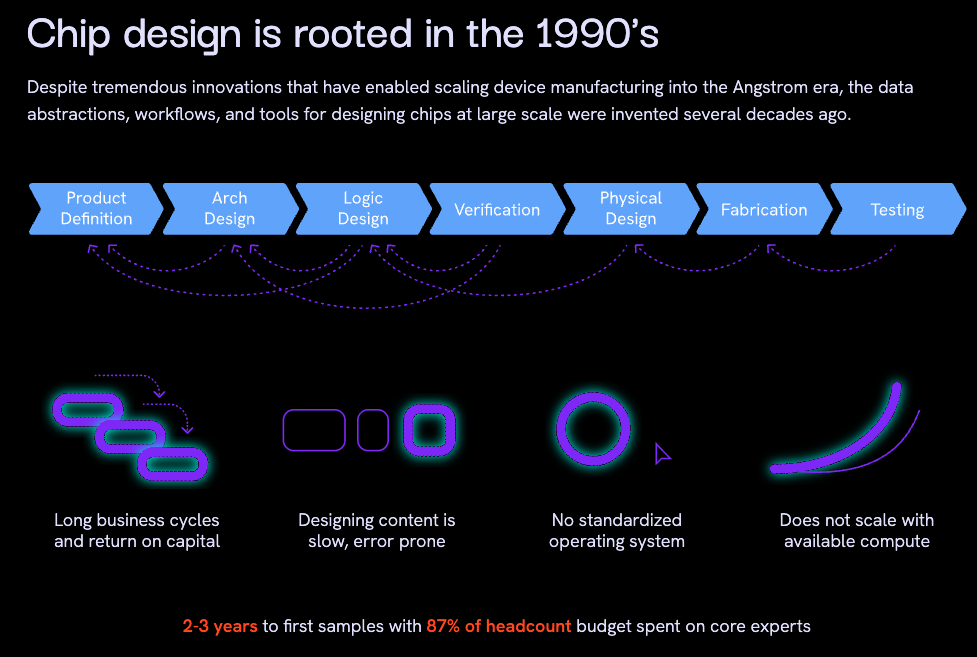

1.半導体産業は構造的課題に直面している

- チップ開発期間:2.5–3年

- 設計初期費用:$200M+(量産含む)

- 専門エンジニア不足

- 検証工数が高すぎる

- ウォーターフォール前提の古いEDA思想が限界

2015年以降、米国で新規ファブレス企業は 年間8社以下しか生まれていない。

これは「設計が難しすぎる・高すぎる」というボトルネックが原因。

2. EDA は進化の上限に到達しつつある

Synopsys や Cadence のツールは強力だが、

プロセス微細化による複雑性増大をアルゴリズム改善だけで追えていない。

つまり市場は「小さな改善」より根本解決を求めている。

-

顧客・競合・パートナー

- 顧客:

- 設計サービス企業、FPGA、ASICメーカー、チップ向け特定IP設計・開発企業

- デジタルIP修正、アナログIPラッピング、FPGA→ASICキャストや次世代半導体設計支援

など多岐にわたる企業が実証中

- パートナー:

- ファウンドリ、EDA企業、IPベンダー、FPGA、ASICベンダーなど

- ファウンドリ、EDA企業、IPベンダー、FPGA、ASICベンダーなど

- 競合:

- Cadence, SynopsysなどのEDA企業やEDA企業向けにAIエンジンを開発している企業など(パートナーにもなりうる)

.svg)